# iMS4-P -xxx (revC) Modular Quad Output Synthesizer

# **Overview and Functions**

#### Models -

| Model  | Outputs | Feature                               | Max Frequency | RF Output |

|--------|---------|---------------------------------------|---------------|-----------|

|        |         |                                       | Range (MHz)   | Power     |

| iMS4-P | 4       | Standard model with USBII,III and GbE | 10 – 225MHz   | 1.2mW     |

Options -xxx

ISOMET CORP, 10342 Battleview Parkway, Manassas, VA 20109, USA.

Tel: (703) 321 8301, Fax: (703) 321 8546, e-mail: isomet@isomet.com

www.ISOMET.com

ISOMET (UK) Ltd, 18 Llantarnam Park, Cwmbran, Torfaen, NP44 3AX, UK.

Tel: +44 1633-872721, Fax: +44 1633 874678, e-mail: isomet@isomet.co.uk

# **Contents**

| 1.  | Hardware Overview and Key features              | 3  |

|-----|-------------------------------------------------|----|

| 2.  | Single (Set Calibration) Tone.                  | 5  |

| 3.  | Local Tone Buffer                               | 5  |

| 4.  | Enhanced Tone Mode (Ramp / Step mode)           | 6  |

| 5.  | Image Mode                                      | 8  |

| 6.  | Look-up-table (LUT).                            | 8  |

| 7.  | RF power Level and Modulation                   | 9  |

| 8.  | Technical Specifications.                       | 10 |

| 9.  | Hardware Connection                             | 12 |

| 10. | Power Amplifier Control                         | 13 |

| 11. | LED Indicators                                  | 14 |

| 12. | Connector pin-outs.                             | 15 |

| 13. | Signal Timing Diagram                           |    |

| 14. | External reference (ERC)                        |    |

| 15. | Software                                        | 22 |

| 16. | Direct programming of the DDS Synthesizer Chip. | 28 |

# **Supporting Documents:**

Setting a static IP Address

Multiple iMS4's on a DHCP Server

iMS4 encoder inputs

iMS4 Isomet GUI Software Guide

iMS4 Compensation LUT Generation rev-C

#### 1. Hardware Overview and Key features.

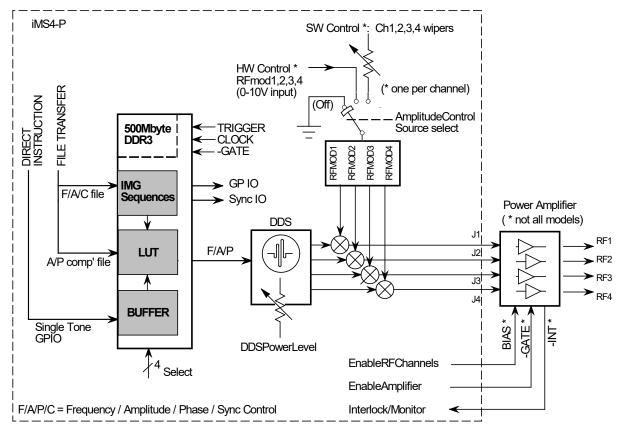

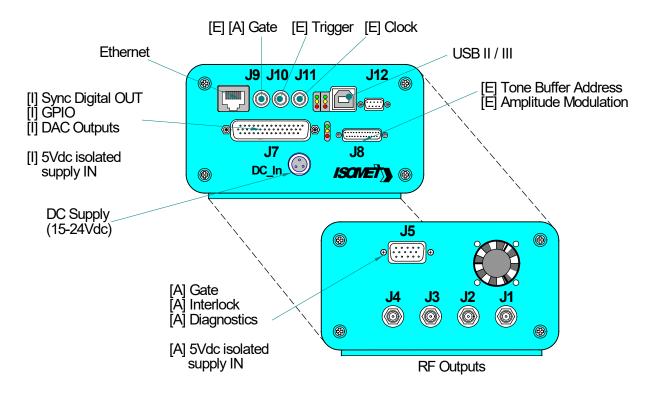

The diagram below illustrates a schematic of the iMS4-P connected with a generic Power Amplifier **Before** operating the IMS4-P, it will be necessary to load the USB Window drivers. (See section 10). The IMS4-P operates from DC power and requires a 15V-24Vdc supply (0.7Aat 24Vdc)

Conceptual diagram for iMS4-P with PA

The iMS4 synthesizer operates in three basic modes

#### 1.1 Local Tone Buffer (LTB) or Single Tone Mode.

This mode is useful for setting the AO Bragg Angle or switching rapidly between 256 preassigned points. The DDS synthesizer generates a single tone output at the specified Frequency, Amplitude and Phase or F/A/P triad.

#### Key features:

- Up to 95 KHz update rate.

- The required output tone may be selected via software control or from hardwired inputs.

- Option to bypass the LUT modifier (see LUT description below)

#### 1.2 IMAGE mode or Sequence mode.

This mode is useful for generating complex scan patterns.

Image files containing the desired frequency scan patterns are downloaded into memory space within the iMS4-P. Output play back is under the control of Trigger and Clock signals provided from an external system or internally generated .

#### Key features:

- Update rate up to 2.0MHz, all four channels.

- Any frequency pattern may be generated e.g. random, linear, step, saw tooth.

- Multiple frequency images can be uploaded, images sequences created, appended, deleted and output order modified.

- Simultaneous upload and play of image files

- Very large image size, in excess of 10million frequency points.

Image and Compensation LUT files (calibration files) can be generated in the GUI supplied with the C++ SDK or on Excel Spread sheet and imported into the C++ project.

#### 1.3 Enhanced tone mode (Ramp / Step mode)

This mode uses the inherent sweep functions built into the DDS chip.

Frequency, amplitude can be ramped in value.

Note: There is no dynamic control of phase or amplitude during a frequency sweep or chirp. The amplitude level remains constant during the sweep duration. There is no phase control, so the benefits of using the Compensation LUT function ( = AOD beam steering) cannot be applied.

#### **Control Features**

#### Look-up-table (LUT)

A calibration or compensation look-up-table (LUT) contains frequency specific phase and amplitude data. Its purpose is to compensate for non-linearity and non-uniformities in the wider system. E.g. create efficient uniform intensity scan lines in an AOD base laser scanning system.

Initial values for the LUT are calculated and loaded into the IMS prior to running the Local Tone Buffer or Image modes. Subsequently, LUT values may be modified with real world measured data or integrated within a feedback mechanism.

#### **Amplitude control**

Each frequency point is assigned a unique 10-bit amplitude value ranging from 0 -100% of the maximum RF power setting. This is a <u>relative value</u> and is dynamic i.e. able to change from output point to output point.

#### **Power Level control**

The maximum RF output power setting is defined by *the* iMS *AmplitudeControl* and *DDSPowerLevel* functions via digital potentiometers. These are 8-bit static controls and together define the <u>absolute</u> RF power level of the IMS4-P (and any connected power amplifier module).

## **Auxiliary Digital and Analog I-O signals**

The iMS-P also features:

| Signal Description                                                     | <u>Ident</u>             |

|------------------------------------------------------------------------|--------------------------|

| 12 bit Synchronous output register, updated with the each new image po | int, SDOR[011]           |

| 4 bits Asynchronous output,                                            | GP Out[13]               |

| 8 bits Asynchronous input,                                             | GP In[18]                |

| 1 bit 24V PLC compatible opto relay output,                            | Laser bit                |

| 4 pairs RS422/encoder differential inputs                              | ENC [(A-P,A-N)(C-P,C-N)] |

|                                                                        |                          |

| 2x Synchronous analog outputs, 0 -5V full scale                        | AOUT_FrqAmp              |

| 1x Asynchronous analog output, 0 -10V full scale                       | AOUT_DAC                 |

| 2x Asynchronous analog inputs, 0 -10V full scale                       | Aux_ADC1 2               |

### Main operating modes and functions.

Please refer to the application program interface (API) documentation with the software development kit (SDK) available as a download.

#### 2. Single (Set Calibration) Tone.

Simplest mode.

Direct programming of the DDS frequency, amplitude and phase values.

Bypasses LUT compensation.

#### 3. Local Tone Buffer.

The Local tone buffer (LTB) area contains a maximum 256 F/A/P locations.

The 256 F/A/P Tones may be rapidly addressed using 8x external LTB address lines or directly from the operating software.

| LTB ext'l address, J8     | Function            | Update rate |

|---------------------------|---------------------|-------------|

| (pins 3,4,5,6,16,14,7,8). |                     |             |

| 0 h FF h                  | Select Tone address | 10.5usec    |

The compensation look up table (see below) may be applied to the Tone Buffer output if required.

#### 4. Enhanced Tone Mode (Ramp / Step mode)

This mode uses the inherent sweep functions built into the DDS chip allowing frequency, amplitude or phase to be ramped in value. However an internal limitation in the DDS chip prevents amplitude ramps in the Enhanced tone mode. Therefore, only frequency ramps and steps will be described.

## 4.1 Ramp Mode

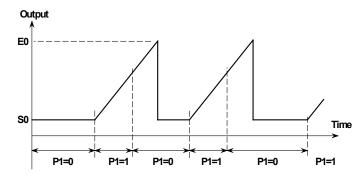

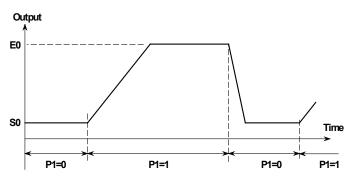

A ramp or chirp is generated by rapidly incrementing the frequency. The number of increment steps and duration of the ramp are user programmable. Each output can be programmed with different ramp parameters.

The ramps are initiated from the GUI or applying a signal to the external Profile inputs on connector J8

#### Available functions:

- Independent Up Down ramp slopes.

- Dwell (stop at end value) or no-dwell (return to start value) at end of sweep duration.

- Set amplitude value for ramp. (remains constant for the ramp duration).

The Ramp mode offers the fastest frequency sweep capability, with a minimum dwell time of 8nsec per frequency increment.

Independent sliders for each of the four output channels define:

- Duration of the rising slope increment.

- Duration of the falling slope increment.

- The number of points for each ramp, up or down.

The falling slope only applies if 'Dwell' is selected in the *Mode* pull down menu.

A **Frequency Sweep no dwell** immediately returns to the start value after the end value has been reached

A **No-Dwell** sweep immediately returns to the **Start** slider value (S0) after the **End** slider value (E0) has been reached

A **Frequency Sweep Dwell** only returns to the start value after a falling edge transition on the appropriate profile input

A *Dwell* sweep only returns to the *Start* slider value (S0) after a falling edge transition on the appropriate profile input

Both plots show a ramp on output J2, controlled using input P1 (on connector J8).

#### 4.2 Step mode

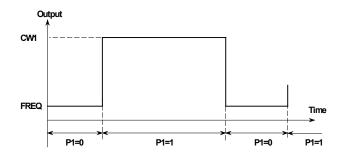

This is essentially a two-level sweep or two-level modulation. Step mode may be applied to the Frequency, Amplitude or Phase. Dwell/No dwell has no function.

Plot shows a frequency step sweep for output J2 controlled using input P1. FREQ = Start Value

CW1 = End Value

## **Amplitude**

The amplitude level across a Frequency or Phase sweep (or step) remains a constant. The value is set by a combination of the **DAC Current** level buttons (Full,  $\frac{1}{2}$ ,  $\frac{1}{4}$ ,  $\frac{1}{8}$ ) and the sliders on the **Signal Path** panel.

#### 5. Image Mode.

An Image contains multiple F/A/P data points pre-arranged to give the desired frequency or scan pattern. Image playback is initiated with the Image Trigger. The output update rate is determined by the Image Clock. The Image trigger and clock may be software generated or applied from an external source. At each clock edge, the next location in the Image Memory area is addressed. The frequency and amplitude data point is read and modified by the LUT data (see below). The resultant F/A/P triad is routed to the DDS registers. An update clock is then issued to the DDS and all 4x RF outputs are simultaneously updated with a new Frequency, Amplitude and Phase value. Any programmed Synchronous control data will also be updated on the appropriate I/O port.

Multiple images can be grouped together into a play sequence. Each image within a sequence can have unique properties such as clock rate and post image delay. Likewise multiple sequences can be defined and queued. These are uploaded into the iMS DDR memory and played in FIFO order. Memory is dynamically allocated to permit flexibility in the size and number of both the images and sequences, and to allow simultaneous upload and output of data. The total number of images (excluding repeats) is 4096. The size of a single image is in excess of a 1million F/A/P points.

#### 6. Look-up-table (LUT).

The LUT is frequency-addressed look-up-table for applying amplitude and phase compensation to the RF signal output. The tables are indexed by the nearest programmed LUT frequency to the demanded output frequency. Table entries are linearly spaced in frequency from the lowest to highest supported. The number of entries in the table is hardware specific. At a minimum, the LUT must contain amplitude compensation data over the desired frequency range of interest.

LUT Size: 2047 entries equally spaced from 10 – 225MHz.

Primary features: Frequency dependent compensation data:

- Amplitude: a value between 0 and 100% for modifying the output amplitude according to frequency. Used for compensating variations in AO efficiency and power amplifier gain.

- Phase: 0 360 degrees. Value represents the phase offset between adjacent channels. Typically applied to beam steered (= phased array) AO deflector designs. Channel 1 is the reference and unmodified. Channel 4 will exhibit the largest phase differential relative to Ch 1.

Secondary features: Synchronous output data

- •Sync Analog: A value between 0.0 and 1.0 that can be output on one of the synchronous DAC outputs (J7). Updated in step with the specified output RF frequency(s).

- •Sync Digital: A binary value that can be output on the synchronous digital outputs. Updated in step with the specified RF output frequency(s).

The Isomet Studio GUI released with SDK v1-7-0 onwards provides a Compensation Function to generate and optimize LUT files. Default LUT files are provided on our website.

## 7. RF power Level and Modulation.

The output RF power at each frequency is determined by the combination of static controls and point specific amplitude data value.

**Static Asynchronous Controls.** Applies to all operating modes.

Purpose: To set the maximum safe operating RF power level.

1: **DDS Power Level**. 8-bit non-volatile digital pot. Always programmed. Sets the DDS chip output level using a dedicated digital pot. Common to all outputs. Typical values 50 – 90%

<< and >>

- 2: Channel Specific *Amplitude Control Source*. This is the control signal source for the RF mixers fitted on each channel. Must select and apply one.

- O1: CH-WIPER1 (2, 3 or 4). An internal 8-bit non-volatile digital pot, one per RF channel.

O0: EXTERNAL signals\*, one per RF channel, output proportional to applied control voltage.

Typical values written and stored to CH-Wiper = 50 – 100%

The above controls should be set in combination so that the AO device is operated at optimum efficiency without saturating the connected power amplifiers and/or applying excessive RF power to the AO device. Starting values will be provided on the appropriate test data sheets

\* Can be wired together to combine multiple channels onto a common control input. 0-10V, 600-ohm / channel. May also used for fast asynchronous amplitude modulation.

#### **Dynamic Synchronous Control.**

Purpose: To set or modulate the RF power at a specific output frequency.

(i.e. to control the diffracted laser intensity at a specific scan angle)

#### 3: Tone Buffer mode

The 10-bit amplitude data value associated with a specific frequency value. This is multiplied by the LUT amplitude calibration factor for that frequency point.

<< or >>

#### 4: Image mode

The 10-bit amplitude data value associated with a specific frequency value. This is multiplied by the LUT amplitude compensation factor for that frequency point.

For a typical AO scanning application, the Image amplitude data is a simple "On" or "Off" value. The LUT is programmed with the variable amplitude compensation data that creates the desired weighting for the scan intensity profile.

In both cases, the LUT can be bypassed if required. The LUT is applied by default.

# 8. Technical Specifications.

# **Image Mode**

| Timing                           | Value                            | Condition                                                                        |

|----------------------------------|----------------------------------|----------------------------------------------------------------------------------|

| Frequency Settling Time          | One cycle at output RF frequency | Step change in Image data value. Phase accumulator re-sync = OFF (default)       |

| Frequency Settling Time          | < 40nsec                         | Step change in Image data value Phase accumulator resync = ON at each clk update |

| Output Delay to Image Clock edge | 1.6 usec                         | * 0.25usec                                                                       |

| Minimum Trigger to Clock edge    | TBD nsec                         |                                                                                  |

| Maximum Image Clock rate         | 2.0 MHz                          | * 3MHz                                                                           |

| Minimum Image Clock rate         | 0 Hz                             |                                                                                  |

| GATE, TRIGGER, CLOCK inputs. J9, J10,J11 | Value     | Condition      |

|------------------------------------------|-----------|----------------|

| Absolute Maximum Input Voltage           | 5.5V      | Per input.     |

| Recommended Input Voltage                | > 3V, <5V | For logic High |

| Minimum Input Voltage                    | 0V        |                |

Active edge of the external Clock or Trigger inputs is user programmable . Default = rising

# **Local Tone Buffer Mode**

| Timing                            | Value  | Condition             |

|-----------------------------------|--------|-----------------------|

| Frequency Settling Time           |        | See Image mode values |

| Output Delay - LTB address change | 6 usec |                       |

| Maximum LTB address rate          | 95KHz  |                       |

| Minimum LTB address rate          | 0 Hz   |                       |

+

| LTB address, input Voltages, J8           | Value      | Condition      |

|-------------------------------------------|------------|----------------|

| Absolute Maximum Input Voltage            | 5.5V       | Per input.     |

| Recommended Input Voltage,                | > 3V, < 5V | For Logic High |

| Minimum Input Voltage                     | 0V         |                |

|                                           |            |                |

| Opto-isolated, signal source sink current | 16mA       | Per input      |

<sup>\*</sup> Future planned optimization. Please contact Isomet

# **External Modulation Inputs, J8**

| Parameter                       | Value    | Condition                                |

|---------------------------------|----------|------------------------------------------|

| RF output Rise time             | < 40nsec | Step change in external modulation input |

| Output Delay - Modulation input | 50nsec   | Step change in external modulation input |

| Absolute Maximum Input Voltage  | 12V      | Per input.                               |

| Recommended Input Voltage       | 10V      |                                          |

| Minimum Input Voltage           | 0V       |                                          |

| Input impedance                 | ~600Ω    | Per input                                |

| On:Off ratio                    | > 35dB   | Full range                               |

| Maximum modulation rate         | 10MHz    |                                          |

| Minimum modulation rate         | 0 Hz     |                                          |

# RF power control, SDK

| Max – Min                                          | Full Range | Condition                        |

|----------------------------------------------------|------------|----------------------------------|

| DDS Power Level                                    | ~ 8dB      | All other variables at max power |

| Amplitude Control Source : Ch-Wiper or Ext'l input | 39dB       |                                  |

| Image or LTB Amplitude data                        | 48dB       | 10bit range                      |

|                                                    |            |                                  |

# RF outputs, J1,J2,J3,J4

| RF Output                    | Full Range      | Condition     |

|------------------------------|-----------------|---------------|

| Maximum frequency range      | 10-225MHz       |               |

| Recommended frequency range  | 20-200MHz       |               |

| Maximum output power         | > 1.2mW / 0.8dB | At 80MHz,     |

| Frequency Stability          | +/- 2.5ppm      | -40C to +85C  |

| Spurious output              | > 40dBc         |               |

| Harmonics                    | > 25dBc         | At 1mW output |

| Channel to Channel Isolation | > 43dB          | At 1mW output |

# Typical output levels at 110MHz, peak-peak voltage, **50ohm** termination

|       |      | Ch1,2,3,4 level / Ext'l modulation Level |       |       |       |      |      |      |      |      |      |

|-------|------|------------------------------------------|-------|-------|-------|------|------|------|------|------|------|

|       | 0%   | 10%                                      | 20%   | 30%   | 40%   | 50%  | 60%  | 70%  | 80%  | 90%  | 100% |

|       | 10%  | 0.006                                    | 0.014 | 0.032 | 0.07  | 0.11 | 0.16 | 0.21 | 0.25 | 0.27 | 0.28 |

|       | 20%  | 0.008                                    | 0.016 | 0.036 | 0.08  | 0.12 | 0.17 | 0.22 | 0.26 | 0.28 | 0.29 |

| _     | 30%  | 0.008                                    | 0.016 | 0.04  | 0.082 | 0.13 | 0.18 | 0.23 | 0.27 | 0.29 | 0.31 |

| Level | 40%  | 0.008                                    | 0.02  | 0.05  | 0.09  | 0.14 | 0.19 | 0.24 | 0.28 | 0.31 | 0.33 |

|       | 50%  | 0.01                                     | 0.03  | 0.06  | 0.1   | 0.15 | 0.21 | 0.26 | 0.3  | 0.33 | 0.35 |

| DDS   | 60%  | 0.01                                     | 0.04  | 0.07  | 0.12  | 0.17 | 0.23 | 0.28 | 0.32 | 0.35 | 0.38 |

| _     | 70%  | 0.02                                     | 0.05  | 0.09  | 0.14  | 0.19 | 0.25 | 0.3  | 0.35 | 0.39 | 0.42 |

|       | 80%  | 0.04                                     | 0.08  | 0.13  | 0.18  | 0.23 | 0.29 | 0.34 | 0.39 | 0.44 | 0.47 |

|       | 90%  | 0.07                                     | 0.13  | 0.19  | 0.25  | 0.3  | 0.36 | 0.41 | 0.47 | 0.53 | 0.57 |

|       | 100% | 0.09                                     | 0.17  | 0.24  | 0.32  | 0.39 | 0.46 | 0.54 | 0.6  | 0.66 | 0.73 |

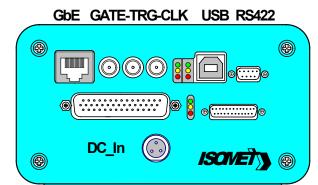

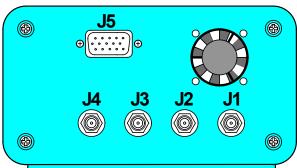

#### 9. Hardware Connection.

#### Minimum Connections:

USB II / III or Ethernet to a host PC.

DC Supply, 15V / 2A minimum to 24V / 1.0A maximum

One or more RF outputs, as required.

#### Recommended channel connections

| AOD / Amplifier Channels | iMS Outputs                           |

|--------------------------|---------------------------------------|

| Single                   | Any                                   |

| Dual                     | J1, J2 or J3, J4                      |

| Quad                     | All, in ascending or descending order |

Optional connections are identified as follows:

- [E] = hardwired control signals from external signal source(s). Functionally equivalent software generated control signal are provided in the SDK.

- [I] = opto-isolated IO buffered signals requiring an external 5Vdc supply connection to J7 or J8

- [A] = external power amplifier connections (see explanation below)

The iMS4-P features external power amplifier diagnostic and control signals.

These are available on J5. J5 will require 5V opto isolator DC feed (5V\_RFA) from the connected RF amplifier. An appropriate interface card must exist within the power amplifier.

## 10. Power Amplifier Control

The iMS4 allows control and diagnostics functions for connected equipment fitted a suitable interface.

#### • Enable/Gate Control

With few exceptions, most Isomet existing power amplifier modules require an active low Gate or Enable signal to operate and will output a normally closed over-temperature thermal interlock signal.

#### Diagnostics

Certain amplifier models feature diagnostic outputs including:

- Forward and reflected RF power (between the PA outputs and connected AO device/load).

- Temperature of the PA

- DC current

- Temperature of the AO device

These are communicated via I2C bus on J5.

## Examples include:

| Model        | Channels | Power/ch  | Frequency Range | Enable/Gate<br>Control | Diagnostics |

|--------------|----------|-----------|-----------------|------------------------|-------------|

| 500C- series | 1        | 2,4,or 7W | Model dependent | NA                     | NA          |

| AF0- series  | 1        | 4 or 7W   | Model dependent | NA                     | NA          |

| AG0- series  | 1        | 1W        | Model dependent | NA                     | NA          |

| AJ0- series  | 4        | 12 or 25W | Model dependent | J5                     | NA          |

| RFA200-2H    | 2        | 100W      | 35 – 65         | J5                     | NA          |

| RFA1170-4    | 4        | 80W       | 48-92           | J5                     | J5          |

| RFA0110-x-20 | 2        | 20W       | 90-130          | J5                     | J5          |

| RFA0120-x-15 | 4        | 15W       | 100-140         | J5                     | J5          |

| RFA0140-x-12 | 4        | 12W       | 120-160         | J5                     | J5          |

NA= not applicable

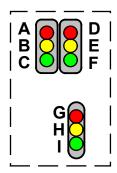

#### 11. LED Indicators.

# **Top Stack, Controller PCB**

| Ident | LED             | Mode                              | iMS4-P                        |

|-------|-----------------|-----------------------------------|-------------------------------|

| Α     | RED (top left)  | If illuminated                    | Not Downloading File          |

| В     | Yellow          | If illuminated                    | Downloading File              |

| С     | Green           | Pulsing                           | Controller OK                 |

| D     | RED (top right) | If illuminated                    | Image output stopped          |

| E     | Yellow          | If illuminated Waiting on Trigger |                               |

| F     | Green           | If illuminated                    | Image playing / output active |

## Lower stack. Synthesizer PCB

| Ident | LED       | Mode        | Stand Alone<br>iMS4- | In combination with PA J5 connected                                       |

|-------|-----------|-------------|----------------------|---------------------------------------------------------------------------|

| G     | RED (top) | Constant on | DC power On          | Thermal Interlock Open (= fault)  or  Gate input (J9) not active (= high) |

| Н     | Yellow    | Constant on | NA                   | PA is enabled. Thermal Interlock OK                                       |

| l     | Green     | Pulsing     | Synthesizer OK       | Synthesizer OK                                                            |

# DC power applied, USB communication problem

If the 6x LED's (A,B,C,D,E,F) are constantly illuminated, then USB communication has not been established. In this case:

a: Ensure USB driver is loaded (see section 10)

b: Cycle DC power

and /or

c: Disconnect then reconnect USB

# 12. Connector pin-outs.

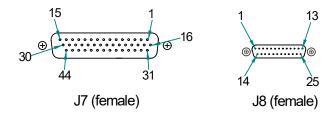

D-type pin idents looking into connector

Front panel view

Pin-out descriptions as follows:

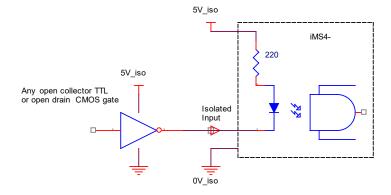

# Circuit details for opto-isolated inputs / outputs on J7 and J8 connector

Recommended drive circuit for opto-isolated logic inputs

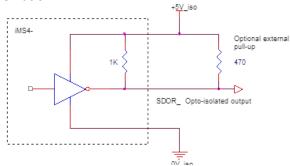

## Opto-isolated logic output schematic

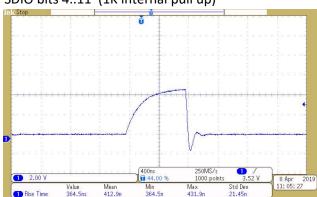

Diagram shown with optional external pull-up resistor to improve the rising edge on SDIO Bits 4..11 Min value 330ohm . Internally fitted on Bits 0..3

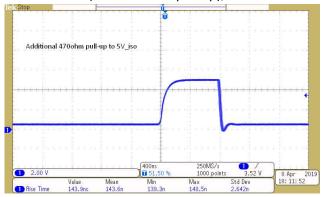

# **SDOR** output trace at **1.2MHz Image clock rate** Default:

SDIO bits 0..3 (330R internal pull up),

SDIO bits 4..11 (1K internal pull up)

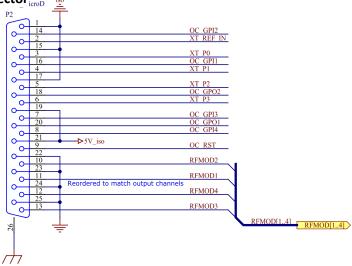

J8, 25way micro-D connector<sub>icroD</sub>

# J8: Main connector for external control signals (Micro-D to full size D-type converter cable available).

| Type          | 25way micro-D                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |            |

|---------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|

| Ident         | J8                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |            |

| Signal        | Typo                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Altornatouso               | Pin        |

| Jigilai       | турс                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Atternate use              | <u> </u>   |

| In            | Analog 0-10V                                             | External amplitude control for M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            | 12         |

|               | <u></u>                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 24         |

| In            |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 13         |

|               |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 25         |

| In            | ·· <del>·</del> ······                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 10         |

| +             |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 22         |

| In            |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 11         |

| +             |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 23         |

|               | 7.110.08                                                 | 7.11.01.08.1.01.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |            |

| In            | Opto isolated logic                                      | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            | 9          |

| In            | Opto isolated logic                                      | Reference Frequency (Optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            | 2          |

|               |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |            |

| In            | Opto isolated logic                                      | Async general purpose input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LTB location/address, bit4 | 16         |

| In            | Opto isolated logic                                      | Async general purpose input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LTB location/address, bit5 | 14         |

| IN            | Opto isolated logic                                      | Async general purpose input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LTB location/address, bit6 | 7          |

| In            | Opto isolated logic                                      | Async general purpose input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LTB location/address, bit7 | 8          |

| Out           | Opto isolated logic                                      | Async general purpose output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | 20         |

| Out           | Opto isolated logic                                      | Async general purpose output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | 18         |

| DC            |                                                          | isolated OV / signal return input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0V                         | 17         |

|               |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |            |

| In            |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 3          |

| In            |                                                          | <u>\</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            | 4          |

| In            | +                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LTB location/address, bit2 | 5          |

| In            | Opto isolated logic                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 6          |

|               |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 1          |

| DC            |                                                          | isolated 0V / signal return input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0V                         | 15         |

| DC            |                                                          | Isolated SV DC supply input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5V output 10mA             | 19         |

|               |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <del> </del>               | 21         |

| DC            |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OV                         | 17         |

|               |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |            |

| 1             |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Key:                       |            |

|               |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |            |

| open collecte | or or open drain gate, 16m<br>ternal 1Kohm pull-up to 5\ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LTB = Local Tone Buffer    |            |

|               | Ident Signal In      | Ident Signal Type  In Analog, 0-10V Analog In Analog In Opto isolated logic Out Opto isolated logic OC  DC  DC  DC  DC  DC  DC  DC  DC  DC | Ident                      | Ident   J8 |

<sup>\*</sup>Note: The external reference clock input (REF\_IN) is not functional on Rev-B

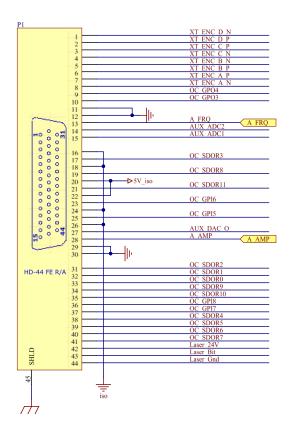

# J7, 44way high density-D connector

Connection for auxiliary I-O signals

| Connector   | Туре   | 44way HD-D            |                                   |               |            |

|-------------|--------|-----------------------|-----------------------------------|---------------|------------|

|             | Ident  | J7                    |                                   |               |            |

| Signal      | Signal | <u>Type</u>           | <u>Description</u>                | Alternate use | <u>Pin</u> |

| Designation |        |                       |                                   |               |            |

| SDOR0       | Out    | Opto isolated logic   | Synchronous-Digital Output bit0   |               | 33         |

| SDOR1       | Out    | Opto isolated logic   | Sync-Digital Output bit1          |               | 32         |

| SDOR2       | Out    | Opto isolated logic   | Sync-Digital Output bit2          |               | 31         |

| SDOR3       | Out    | Opto isolated logic   | Sync-Digital Output bit3          |               | 17         |

| SDOR4       | Out    | Opto isolated logic   | Sync-Digital Output bit4          |               | 38         |

| SDOR5       | Out    | Opto isolated logic   | Sync-Digital Output bit5          |               | 39         |

| SDOR6       | Out    | Opto isolated logic   | Sync-Digital Output bit6          |               | 40         |

| SDOR7       | Out    | Opto isolated logic   | Sync-Digital Output bit7          |               | 41         |

| SDOR8       | Out    | Opto isolated logic   | Sync-Digital Output bit8          |               | 19         |

| SDOR9       | Out    | Opto isolated logic   | Sync-Digital Output bit9          |               | 34         |

| SDOR10      | Out    | Opto isolated logic   | Sync-Digital Output bit10         |               | 35         |

| SDOR11      | Out    | Opto isolated logic   | Sync-Digital Output bit11         |               | 21         |

| D_Rtn       | Out    |                       | isolated 0V / signal return input | 0V            | 26         |

| ENC_D_N     | In     | 5V differential logic | Encoder Input N, Channel D        |               | 1          |

| ENC_D_P     | In     | 5V differential logic | Encoder Input P                   |               | 2          |

| ENC_C_P     | In     | 5V differential logic | Encoder Input P, Channel C        |               | 3          |

| ENC_C_N     | In     | 5V differential logic | Encoder Input N                   |               | 4          |

| ENC_B_N     | In     | 5V differential logic | Encoder Input N, Channel B        |               | 5          |

| ENC_B_P     | In     | 5V differential logic | Encoder Input P                   |               | 6          |

| ENC_A_P     | In     | 5V differential logic | Encoder Input P, Channel A        |               | 7          |

| ENC_A_N           | In             | 5V differential logic         | Encoder Input N                             |                      | 8  |

|-------------------|----------------|-------------------------------|---------------------------------------------|----------------------|----|

| D_Rtn             | In             | (5V_iso supply required)      | isolated 0V / signal return input           | 0V                   | 16 |

|                   |                |                               |                                             |                      |    |

| GP I5             | In             | Opto isolated logic           | Asynchronous GP logic input                 |                      | 25 |

| GP 16             | In             | Opto isolated logic           | Async GP input                              |                      | 23 |

| GP 17             | In             | Opto isolated logic           | Async GP input                              |                      | 37 |

| GP 18             | In             | Opto isolated logic           | Async GP input                              |                      | 36 |

| GP 03             | Out            | Opto isolated logic           | Async GP logic output                       |                      | 9  |

| GP O4             | Out            | Opto isolated logic           | Async GP output                             |                      | 10 |

| D_Rtn             | Out            |                               | isolated 0V / signal return input           |                      | 24 |

| 24V_laser         | In             | PLC                           | Laser Opto-Supply                           |                      | 42 |

| Laser_Bit         | Out            | PLC                           | Laser Opto relay bit Tr/Tf < 50usec)        |                      | 43 |

| Gnd_laser         | In             | PLC                           | Laser Opto-Gnd                              |                      | 44 |

| AOUT_Frq          | Out            | Analog                        | 8-bit analog representation of Image freq   |                      | 13 |

| AOUT_Amp          | Out            | Analog                        | 8-bit analog equivalent of Image amplitude  |                      | 28 |

| A_Rtn             | Out            | Analog                        | Analog return                               |                      | 30 |

| AOUT_DAC          | Out            | Analog                        | GP 12-bit DAC analog output.                |                      | 27 |

| A_Rtn             | Out            | Analog                        | Analog return                               |                      | 29 |

| Aux_ADC1          | In             | Analog                        | GP Analog input to a 12-bit ADC (0 to 10V). |                      | 15 |

| A_Rtn             | In             | Analog                        | Analog return                               |                      | 11 |

| Aux_ADC2          | In             | Analog                        | GP Analog input to a 12-bit ADC (0 to 10V). |                      | 14 |

| A_Rtn             | In             | Analog                        | Analog return                               |                      | 12 |

| 5V_iso            | DC             |                               | Isolated 5V DC supply input                 | 5V output, 10mA      | 22 |

| 5V_iso            | DC             |                               | Isolated 5V DC supply input                 | 5V output, 10mA      | 20 |

| D_Rtn             | DC             |                               | isolated 0V / signal return input           | 0V                   | 18 |

| Notes:            |                |                               |                                             | Кеу:                 |    |

| Type Logic = TTL  | or 5V CMOS     |                               |                                             | GP = General Purpose |    |

| Drive inputs with | open collect   | or or open drain gate, 16mA : | sink                                        |                      |    |

| Open collector or | utputs with in | iternal 1Kohm pull-up to 5V_i | so                                          |                      |    |

# **Other Connectors**

| Connector               | Туре      | see table            |                                        |               |                   |              |              |

|-------------------------|-----------|----------------------|----------------------------------------|---------------|-------------------|--------------|--------------|

|                         | Ident     | see table            |                                        |               |                   |              |              |

| Signal                  | Signal    |                      | Description                            | Alternate use | Connector         | Ident        | <u>Pin</u>   |

| Designation Designation | Jigilai   | <u> 1 y p c</u>      | <u> </u>                               | Alternate ase | COMMECTOR         | iuciic       | <del> </del> |

|                         |           |                      | Communication                          |               | <b></b>           |              |              |

| Ethernet                | In/Out    | Logic                | GbE                                    |               | RJ45              |              |              |

| USB Serial              | In/Out    | Logic                | USB II / USBIII                        |               | B-type            | -            |              |

|                         |           |                      |                                        |               |                   |              |              |

| RX-P                    | In        | Logic                | RS422 receive+                         |               | 9-way D           | J12          | 2            |

| RX-N                    | In        | Logic                | RS422 receive-                         |               | 9-way D           | J12          | 1            |

| TX-P                    | Out       | Logic                | RS422 transmit+                        |               | 9-way D           | J12          | 7            |

| TX-N                    | Out       | Logic                | RS422 transmit-                        |               | 9-way D           | J12          | 6            |

| Rtn                     | Gnd       |                      | Sig Rtn                                |               | 9-way D           | J12          | 5            |

|                         |           |                      |                                        |               |                   |              |              |

|                         |           |                      | DC Supply                              |               |                   |              |              |

| Vdc                     | DC        | DC-In                | Supply 15V -24V dc, <0.4A              |               | 3w TINI-Q         |              | 1            |

|                         | 0V        | DC-In                |                                        |               | 3w TINI-Q         |              | 2            |

|                         | -         |                      | SMA Coax Connections                   |               |                   | ļ            | <del> </del> |

| Cato                    | In        | Logic                | ······································ | DOE input     | SMA coaxial       | J9           | Centre       |

| Gate<br>Rtn             | In<br>Gnd | Logic                | Enable power amplifiers via J5 Sig Rtn | POF input     | SIVIA COAXIAI     | J9           | Outer        |

| NUI                     | Gilu      |                      | - Sig Kui                              |               |                   | <del> </del> | Outer        |

| Trigger                 | In        | Logic                | Trigger Image Data Output              | POF input     | SMA coaxial       | J10          | Centre       |

| Rtn                     | Gnd       | LOGIC                | Sig Rtn                                | 1 Of Input    | JIVIA COBAIGI     | 310          | Outer        |

| 11(11                   | Gild      |                      | Jig Kui                                |               |                   |              | Outer        |

| Clock                   | In        | Logic                | Clock Image Data                       | POF input     | SMA coaxial       | J11          | Centre       |

| Rtn                     | Gnd       | 20810                | Sig Rtn                                | - Compac      | - Sivii ( Couxiui | 1            | Outer        |

|                         | Gild      |                      | Jig Kui                                |               |                   |              | Outer        |

| Ch0                     | Analog    | RF                   | RF1 frequency output, 50Ω              |               | SMA coaxial       | J1           | Centre       |

| Rtn                     | Gnd       | 111                  | Sig Rtn                                |               | JIVIA COUXIGI     | 31           | Outer        |

| Ch1                     | Analog    | RF                   | RF2 frequency output, 50Ω              |               | SMA coaxial       | J2           | Centre       |

| Rtn                     | Gnd       | 111                  | Sig Rtn                                |               | JIVIA COUXIGI     | 32           | Outer        |

| Ch2                     | Analog    | RF                   | RF3 frequency output, 50Ω              |               | SMA coaxial       | J3           | Centre       |

| Rtn                     | Gnd       | 1/1                  | Sig Rtn                                |               | JIVIA COBAIDI     | - 33         | Outer        |

| Ch3                     | Analog    | RF                   | RF4 frequency output, $50\Omega$       |               | SMA coaxial       | J4           | Centre       |

| Rtn                     | Gnd       | NI                   | Sig Rtn                                |               | SIVIA COAXIAI     | J4           | Outer        |

| 11(11                   | Gild      |                      | Jig Kui                                |               |                   |              | Outer        |

|                         |           |                      | J5 Power Amp Control *                 |               |                   |              |              |

| 5V_RFA                  | In        |                      | Opto supply from connected PA          | 5V, 20mA out  | 15w-HD D          | J5           | 1            |

| 5V RFA                  | In        |                      | Opto supply from connected PA          | 5V, 20mA out  | 15w-HD D          | J5           | 10           |

| OV RFA                  | In        |                      | Opto 0V from connected PA              | OV            | 15w-HD D          | J5           | 4            |

| OV RFA                  | In        |                      | Opto 0V from connected PA              | OV            | 15w-HD D          | J5           | 7            |

|                         |           |                      |                                        |               |                   |              |              |

| SCL_RFA_TX              | 10        | Opto isolated logic  | I2C Clock_TX                           |               | 15w-HD D          | J5           | 2            |

| SCL_RFA_RX              |           | Opto isolated logic  | I2C Clock_RX                           |               | 15w-HD D          | J5           | 3            |

| SDA_RFA_TY              | 10        | Opto isolated logic  | I2C Data_TY                            |               | 15w-HD D          | J5           | 5            |

| SDA_RFA_RY              |           | Opto isolated logic  | I2C Data_RY                            |               | 15w-HD D          | J6           | 6            |

| TVT CONVCT              | 0         | Onto icolate d la a' | Stort ADC conversion                   |               | 15 U.D. D.        | ļ            |              |

| EXT-CONVST              | Out       | Opto isolated logic  | Start ADC conversion                   |               | 15w-HD D          | J5           | 8            |

| -EXT_GATE               | Out       | Opto isolated logic  | Enable connected amplifier             |               | 15w-HD D          | J5           | 9            |

| EXT-BSY                 | ln .      | Opto isolated logic  | ADC conversion busy                    |               | 15w-HD D          | J5           | 11           |

| EXT-INT MON             | ln        | Opto isolated logic  | Interlocks valid monitor               |               | 15w-HD D          | J5           | 12           |

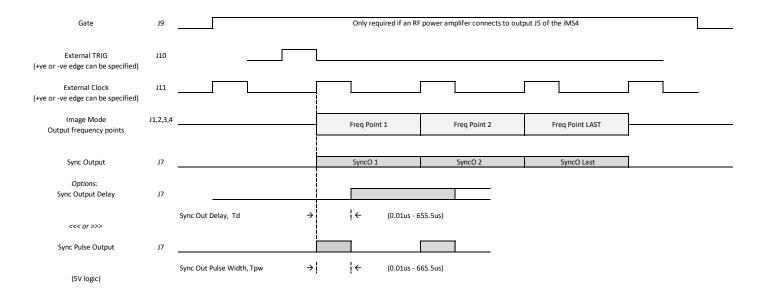

#### 13. Signal Timing Diagram

Applies to Image mode.

NOTE: For clarity, the 1.6usec latency between the External clock and the respective Output frequency point is not shown. This is a static delay and does not impact on Image Clock rate.

## 14. External reference (ERC)

iMS4- revC models employ a PLL to generate the system clock for the DDS chip, AD9959. By default, an internal 25MHz TCXO connects to the PLL reference clock input. Optionally, the user can provide an external reference clock on pin 2 (sig) / pin 1 (rtn) of J8. Contact Isomet for guidance to enable this option.

The ERC input requires a positive going digital signal and is 50 ohm terminated.

The signal is routed to a 5V tolerant buffer and then a digital isolator.

The buffer and digital isolator operate from an isolated 5V supply which the user needs to provide on pin 21 (+5V) / pin 17 (0V) of J8

## Reference Clock:

Frequency: Any multiple of 20KHz

Minimum 40KHz Maximum 16MHz

Voltage: Positive only, 50ohm input impedance

Minimum 1.25V Maximum 5.0V

#### 15. Software.

The core of the Software Development Kit is the C++ iMS library and API. All interaction with iMS hardware ultimately passes through this API. However we have also provided a number of other software utilities and wrappers that allow you to use the iMS System at a higher level of abstraction.

Included in the SDK are:

- •The core iMSLibrary binaries for a number of different platforms and toolsets.

- Accompanying C++ header files for application interface.

- •iMSNET An experimental .NET assembly written in C# that wraps the core library and permits user application development in any .NET language targeting the .NET Framework

- ims\_hw\_server is a command line daemon type process that can handle all communication with an iMS system, decoupling it from user application business logic. A gRPC streaming interface connects the server to application software, either on the same host or across a network.

- •iMS Studio is a full featured GUI front end application that can be used to create Images, Tone Buffers and Compensation Functions and play them on an iMS system. This is often a good starting point for users wishing to explore the capabilities of an iMS before starting development of custom software.

The iMS software is available for download from <a href="http://www.isomet.com/software.html">http://www.isomet.com/software.html</a>

Depending on your computer select and run one of the following:

Isomet iMS SDK v 1.x.x Win7 Setup.exe Isomet iMS SDK v 1.x.x Win10 Setup.exe

The software download also includes documentation and tutorials for setting up a project and connecting to the iMS. Note: these Tutorials are NOT specific to any practical AO device.

Please refer to Quick Start Guide: Isomet iMS Studio for instructions on the Isomet Windows GUI

The iMS software library and API has been written purely in native ANSI-C++ with some use of features introduced in C++11 (ISO/IEC 14882:2011), including the C++ Standard Library. There is no use of features associated with the updated C++14 specification.

Isomet will provide example projects applicable to the customer hardware configuration.

The Software Development Kits are regularly updated. Please check for Isomet website for updates.

#### **Visual Studio Notes**

|                                                  | Visual Studio 20                            | 13 (v120) | Visual Studio 20 | 15 (v140) |

|--------------------------------------------------|---------------------------------------------|-----------|------------------|-----------|

|                                                  | <ul> <li>★</li> <li>✓</li> <li>Δ</li> </ul> | 64-bit    | 32-bit           | 64-bit    |

| Microsoft Windows<br>2000/XP/Vista or<br>earlier | ×                                           | *         | ×                | ж         |

| Microsoft Windows<br>7 Professional              | 1                                           | 1         | 1                | 1         |

| Microsoft Windows<br>8/8.1                       | Δ                                           | Δ         | <b>A</b>         | Δ         |

| Microsoft Windows<br>10 Professional             | ×                                           | *         | 1                | 1         |

Table 1 Toolset Version Compatibility Table

#### b. Folder locations.

For ease of installation, a C++ console application template file is provided.

Copy the file iMSTemplateWin7VC140.zip into the Visual Studio project templates folder e.g. C.....Documents > Visual Studio 2015 > Templates > ProjectTemplates

DO NOT unzip

When starting New Project from Visual Studio, the iMS Console Application will be offered Edit the project *Location* as required.

However Rename in VCPP Solution Explorer window after Template project is started.

## c. Adding C++ code to the project template

Please refer to the comments within the C++ template code and the ReadMe.txt file

The application includes the example code necessary for connection to the iMS4 (via selected ports) and files which are used to build a precompiled header (PCH) file; StdAfx.h, StdAfx.cpp

# Add additional include files to StdAfx.h

Referencing the default Source file (e.g. iMSTemplate.cpp)

User application code is added from line 111

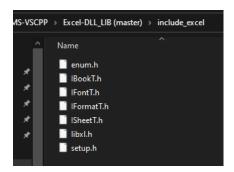

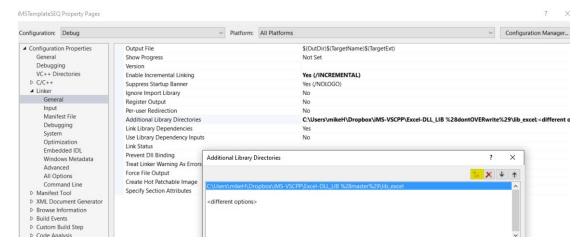

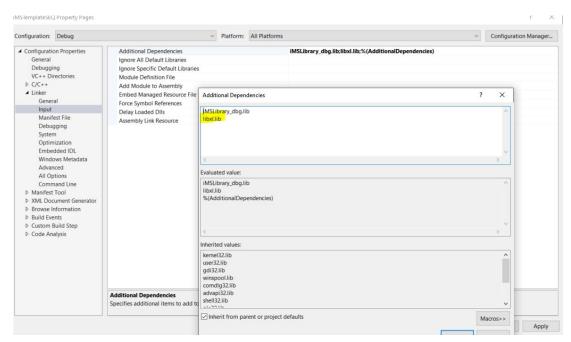

# d. Installing the 3<sup>rd</sup> party Excel Spreadsheet Import Export function

Generating Compensation Tables (LUTs) and Image files in Excel can be convenient. Several routines exist to import data into C++. One such is from libxl.com A licence key is required and it is free to use.

Add the following code prior to calling the LibXL functions.

// call LibXL licence key libxl::Book\* ExcelBook = xlCreateBook(); ExcelBook->setKey(L"Michael Hillier", L"windows-222329040ec5ec046fb46767a7h1gej6");

To add this feature to your project

Create a folder Excel-DLL LIB in the Projects folder and download associated files (contact Isomet)

Copy the include files from include\_excel folder to MS VS installed folder

e.g. to C:\Program Files (x86)\Microsoft Visual Studio 14.0\VC\include

(Subsequently if using the Isomet template project, add additional include files to **StdAfx.h** only)

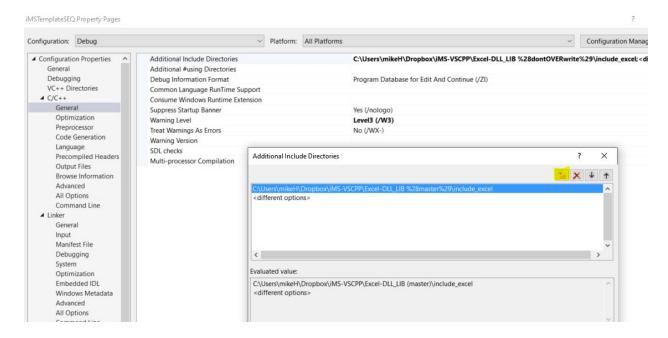

Add 'include\_excel' to the Additional Include Directory under C++ > General.

• Copy libxl.dll from > Excel\_DLL-LIB > bin to the project folder you created.

It must be in the same folder as the source file \*.cpp.

• Add the folder containing libxl.lib to the *Additional Library Dependencies* under *Linker > General*.

• Add libxl.lib to the Additional Dependencies under Linker > Input

• To implement the above , hit Apply

## 16. Direct programming of the DDS Synthesizer Chip.

For most applications, the use of the DDSscript function is not required (C++ only)

#### **Use with CAUTION**

The DDS IC that generates the RF signals can be manually programmed to access advanced features that wouldn't normally be available through the iMS API. To do this requires a detailed knowledge and understanding of the Analog Devices AD9959 Frequency Synthesiser IC and its register map.

If it is necessary to manually program the AD9959, a sequence of register writes can be generated (called a DDS Script) and stored in the Synthesiser Filesystem. The application software may then recall the script from the filesystem and execute it to commit the register writes to the AD9959. Please refer to DDSscript Class description in the SDK documentation.

#### **REGISTER MAPS**

Each register write is initialised with the name of the register as the first argument. (This is in the same abbreviated form as specified in the AD9959 datasheet).

## **Control Register Map**

| Register<br>Name                      | Bit<br>Range | Bit 7<br>(MSB)                                    | Bit 6                                      | Bit 5                                             | Bit 4                                                | Bit 3                | Bit<br>2 | Bit1                       | Bit 0<br>(LSB) | Default<br>Value    |